Publications

Selected publications by HUEDA Research Group

2025

A Novel Heuristic Neuron Grouping Algorithm for Deep Neural Network Accelerators

Cakin, A., Dilek, S., Tosun, S., Nacar, F.

Published in Journal of Circuits, Systems and Computers

Abstract

Deep neural networks (DNNs) have witnessed widespread adoption across various domains. However, their computational demands pose significant challenges due to the extensive inter-neuron communication within the network. Moreover, the energy consumption of DNNs is substantial, primarily driven by the vast data movement and computational requirements. To overcome these challenges, novel accelerator architectures are essential. In this study, we present a novel heuristic algorithm for neuron grouping, catering to both fully connected and partially pruned DNN models. Our algorithm aims to minimize the overall data communication cost among neuron groups while also considering computational load balance. It outperforms existing heuristic neuron grouping methods classified into three main approaches from the literature by an average improvement in communication cost ranging from 33.01% to 47.11%. By optimizing neuron grouping, our approach may be used to enhance the efficiency of DNN accelerators, enabling improved performance and reduced energy consumption.

DOI: 10.1142/S0218126625501786

How to cite (BibTeX)

@article{doi:10.1142/S0218126625501786,

author = {Cakin, Alperen and Dilek, Selma and Tosun, Suleyman and Nacar, Furkan},

title = {A Novel Heuristic Neuron Grouping Algorithm for Deep Neural Network Accelerators},

journal = {Journal of Circuits, Systems and Computers},

volume = {34},

number = {07},

pages = {2550178},

year = {2025},

doi = {10.1142/S0218126625501786},

URL = {

https://doi.org/10.1142/S0218126625501786

},

eprint = {

https://doi.org/10.1142/S0218126625501786

}

}

2024

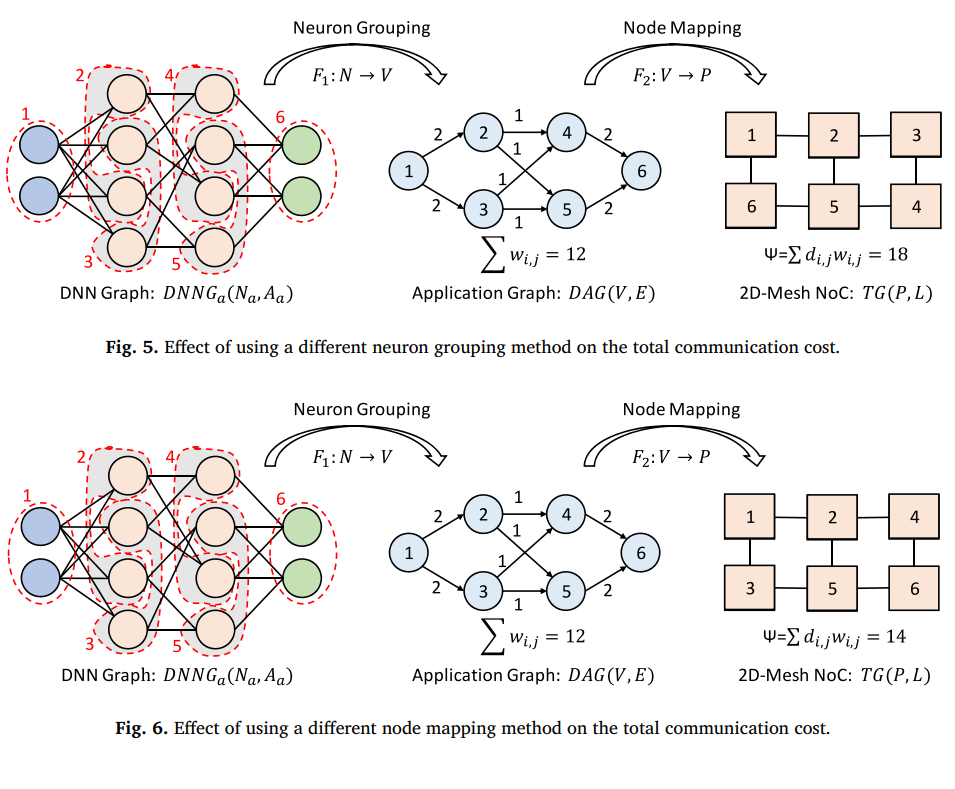

Neuron grouping and mapping methods for 2D-mesh NoC-based DNN accelerators

Nacar, F., Cakin, A., Dilek, S., Tosun, S., Chakrabarty, K.

Published in Journal of Parallel and Distributed Computing

Abstract

Deep Neural Networks (DNNs) have gained widespread adoption in various fields; however, their computational cost is often prohibitively high due to the large number of layers and neurons communicating with each other. Furthermore, DNNs can consume a significant amount of energy due to the large volume of data movement and computation they require. To address these challenges, there is a need for new architectures to accelerate DNNs. In this paper, we propose novel neuron grouping and mapping methods for 2D-mesh Network-on-Chip (NoC)-based DNN accelerators considering both fully connected and partially connected DNN models. We present Integer Linear Programming (ILP) and simulated annealing (SA)-based neuron grouping solutions with the objective of minimizing the total volume of data communication among the neuron groups. After determining a suitable graph representation of the DNN, we also apply ILP and SA methods to map the neurons onto a 2D-mesh NoC fabric with the objective of minimizing the total communication cost of the system. We conducted several experiments on various benchmarks and DNN models with different pruning ratios and achieved an average of 40-50% improvement in communication cost.

DOI: 10.1016/j.jpdc.2024.104949

How to cite (BibTeX)

@article{NACAR2024104949,

title = {Neuron grouping and mapping methods for 2D-mesh NoC-based DNN accelerators},

journal = {Journal of Parallel and Distributed Computing},

volume = {193},

pages = {104949},

year = {2024},

issn = {0743-7315},

doi = {https://doi.org/10.1016/j.jpdc.2024.104949},

url = {https://www.sciencedirect.com/science/article/pii/S0743731524001138},

author = {Furkan Nacar and Alperen Cakin and Selma Dilek and Suleyman Tosun and Krishnendu Chakrabarty}

}

2024

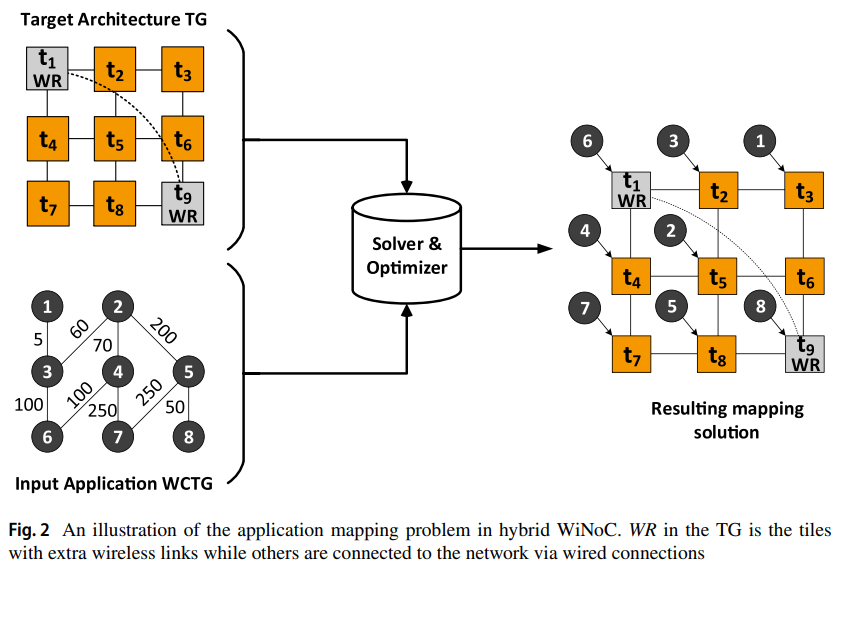

Energy-aware application mapping methods for mesh-based hybrid wireless network-on-chips

Cakin, A., Dilek, S. & Tosun, S.

Published in Journal of Supercomputing

Abstract

The 2D mesh topology-based Network-on-Chip (NoC) is a prevalent structure in System-on-Chip (SoC) designs, offering implementation and fabrication benefits. However, increased NoC scale leads to longer communication paths, more hops, and higher end-to-end latency and energy consumption. To mitigate these issues, Wireless NoC (WiNoC) integrates wireless communication, enhancing data rates, energy efficiency, and routing flexibility. Despite several mapping algorithms for NoCs, optimal techniques for hybrid WiNoCs are underexplored. This study proposes two novel application mapping methods for 2D mesh topology-based hybrid WiNoCs, using quadratic programming (QP) and simulated annealing (SA). Our goal is to minimize communication-related energy consumption. We evaluated these methods across various wireless router configurations, benchmarks, and custom application graphs. The QP-based method excels in smaller problems, while the SA-based approach yields optimal or near-optimal results for larger sizes within practical runtimes.

DOI: 10.1007/s11227-024-06062-4

How to cite (BibTeX)

@Article{Cakin2024,

author={Cakin, Alperen

and Dilek, Selma

and Tosun, Suleyman},

title={Energy-aware application mapping methods for mesh-based hybrid wireless network-on-chips},

journal={The Journal of Supercomputing},

year={2024},

month={Jul},

day={01},

volume={80},

number={11},

pages={15582-15612},

issn={1573-0484},

doi={10.1007/s11227-024-06062-4},

url={https://doi.org/10.1007/s11227-024-06062-4}

}

2023

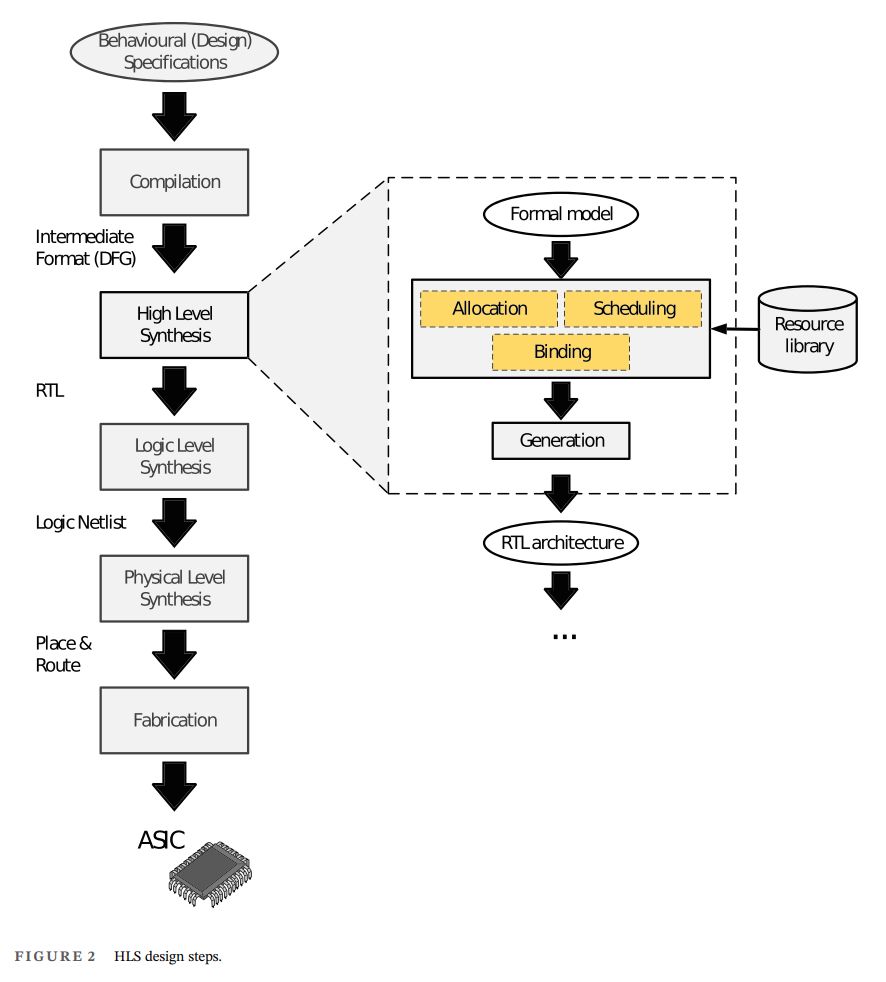

Simulated annealing-based high-level synthesis methodology for reliable and energy-aware ASIC designs

Dilek, S, Tosun, S, Cakin, A.

Published in International Journal of Circuit Theory and Applications

Abstract

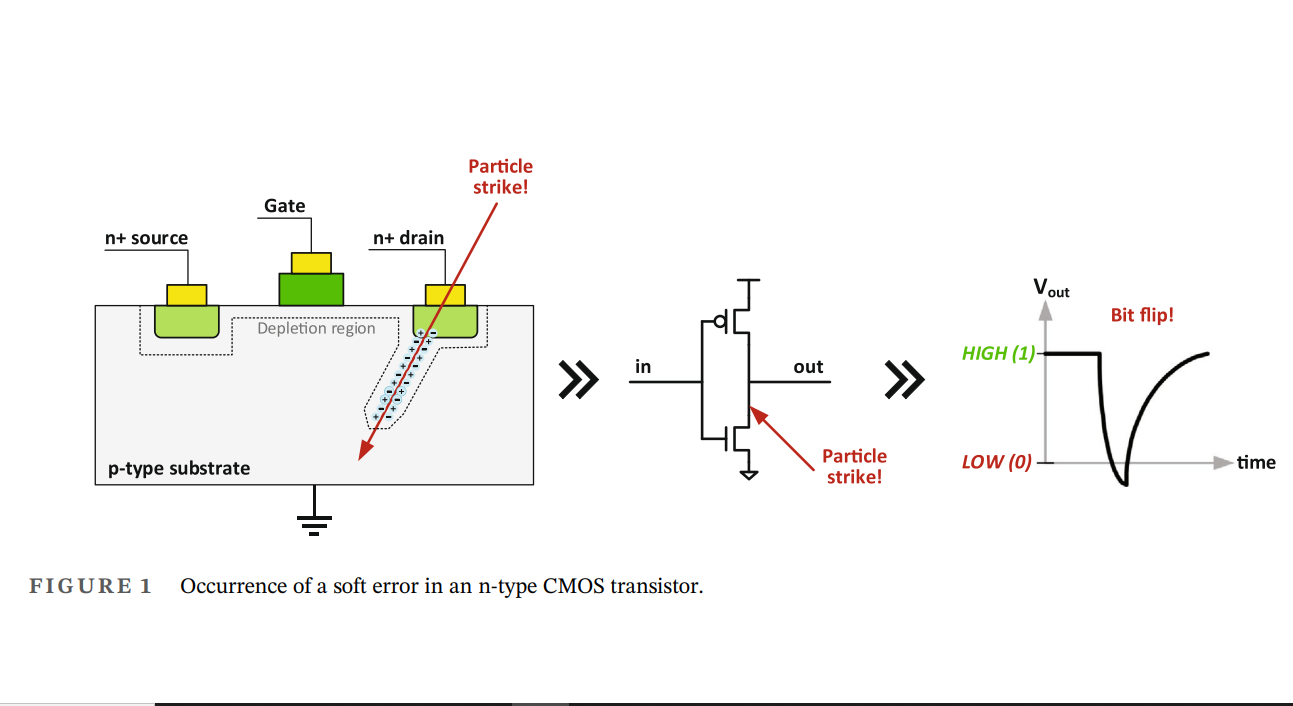

Summary Integrated circuits have become more vulnerable to soft errors due to smaller transistor sizes and lower threshold voltage levels. Energy reduction methods make circuits more error-prone since even the smallest amounts of environmental radiation can cause a bit flip. Furthermore, redundancy-based error detection and correction methods induce higher costs and area overhead. Thus, several conflicting parameters may need to be considered during embedded system design (e.g., area, performance, energy, and reliability). High-level synthesis (HLS) is the most practical design step to consider all these parameters as complexity increases at lower levels. HLS can be viewed as a multi-objective optimization problem of finding a set of Pareto-optimal designs, allowing designers to choose the ones that best fit the requirements. Moreover, the number of synthesis options superlinearly affects the search space growth, necessitating efficient optimization methods. In this study, we propose simulated annealing (SA)-based HLS methods for multi-Vcc application-specific integrated circuit design, aiming to optimize energy consumption and reliability under the area and latency constraints. Furthermore, we use duplication to improve design reliability as much as the constraints allow. We compared our methods against genetic algorithm (GA)-based and integer linear programming (ILP)-based methods and showed their effectiveness in finding optimum or near-optimum results in a short running time. SA-based methods achieved up to 21.20\% reliability improvement on average and up to 38\% energy reduction on average, while preserving the reliability value against the GA-based metaheuristic counterpart under joint reliability and energy optimization on four HLS benchmarks.

DOI: 10.1002/cta.3666

How to cite (BibTeX)

@article{https://doi.org/10.1002/cta.3666,

author = {Dilek, Selma and Tosun, Suleyman and Cakin, Alperen},

title = {Simulated annealing-based high-level synthesis methodology for reliable and energy-aware application specific integrated circuit designs with multiple supply voltages},

journal = {International Journal of Circuit Theory and Applications},

volume = {51},

number = {10},

pages = {4897-4938},

keywords = {application-specific integrated circuits, energy, high-level synthesis, modular redundancy, optimization, reliability, simulated annealing, soft errors, voltage islands},

doi = {https://doi.org/10.1002/cta.3666},

url = {https://onlinelibrary.wiley.com/doi/abs/10.1002/cta.3666},

eprint = {https://onlinelibrary.wiley.com/doi/pdf/10.1002/cta.3666},

year = {2023}

}

2022

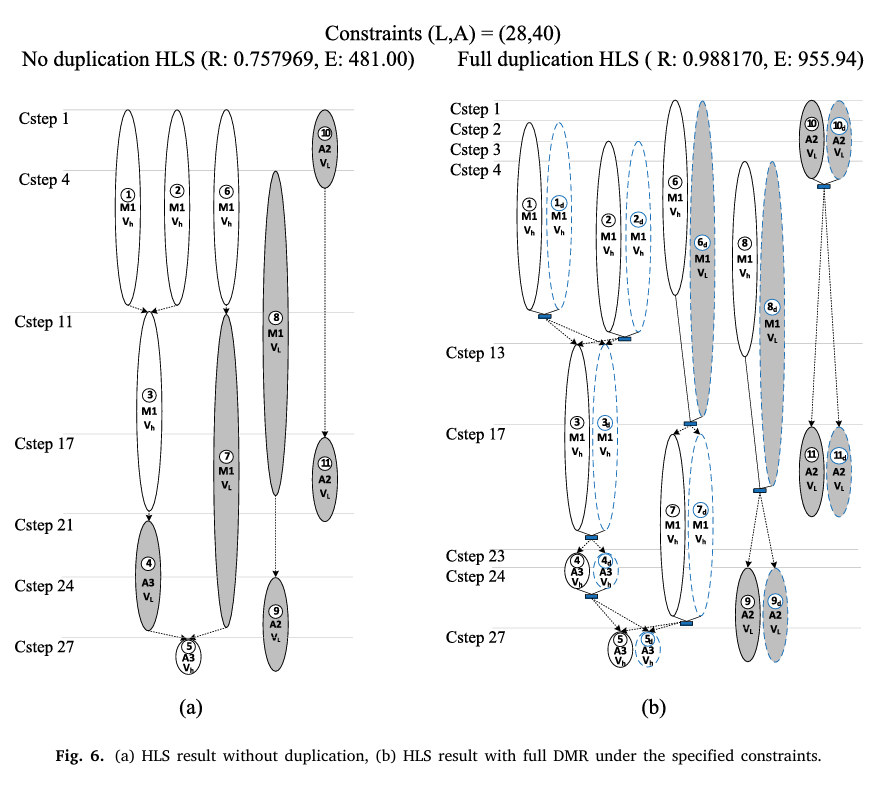

Integer linear programming-based optimization methodology for reliability and energy-aware high-level synthesis

Dilek, S, Tosun, S.

Published in Microelectronics Reliability.

Abstract

Continuous decrease in the transistor technology sizes has enabled much denser packaging of electronic components on chips, which has resulted in integrated circuits with lower costs and area. However, it has also given rise to new issues and challenges in the process of integrated circuit design, including higher vulnerability to soft errors. Modular hardware redundancy is a popular method for improving the reliability of a system against errors at a cost of increasing area and energy consumption. Voltage scaling methods can be employed to tackle high energy costs; however, this also negatively affects the circuit’s reliability and performance. Therefore, designing circuits with all these conflicting parameters is a very challenging task. In this study, we propose integer linear programming (ILP)-based high-level synthesis (HLS) methods to optimize both reliability and/or energy under the area and latency constraints. Our models employ full and partial duplication to improve the system reliability as long as the area constraint permits. They also utilize voltage islands as the energy reduction method of choice. What makes this problem even more interesting and complex is the fact that we use different versions of the same resources that have different area, latency, reliability, and energy values. Although this affects the execution time of the proposed methods, it also gives us more design options. We compared and showed the effectiveness of our methods against a genetic algorithm-based one on several HLS benchmarks. The ILP-based methods return the optimum results most of the time under the given time limits.

DOI: 10.1016/j.microrel.2022.114849

How to cite (BibTeX)

@article{DILEK2022114849,

title = {Integer linear programming-based optimization methodology for reliability and energy-aware high-level synthesis},

journal = {Microelectronics Reliability},

volume = {139},

pages = {114849},

year = {2022},

issn = {0026-2714},

doi = {https://doi.org/10.1016/j.microrel.2022.114849},

url = {https://www.sciencedirect.com/science/article/pii/S0026271422003821},

author = {Selma Dilek and Suleyman Tosun}

}

2022

A High-Level Synthesis Methodology for Energy and Reliability-Oriented Designs

Dilek, S., Smri, R., Tosun, S., Dal, D.

Published in IEEE Transactions on Computers

Abstract

Shrinking technology sizes of the CMOS circuits makes it possible to place more transistors on a single chip at each technology generation. On the other hand, circuits become more vulnerable to radiation effects due to lower supply and threshold voltage levels; thus, the number of transient faults in circuits tends to increase. Moreover, energy reduction techniques also negatively affect the reliability of circuits. Traditional high-level synthesis (HLS) methods usually consider only area and latency along with either energy or reliability. Especially the effect of using different voltage levels on reliability is completely ignored by previous studies. In this article, we present two new HLS methods for application-specific integrated circuit (ASIC) design under area and timing constraints with the objectives of low energy consumption and high reliability. For the mapping and scheduling steps of HLS, we propose integer linear programming (ILP) and genetic algorithm (GA)-based optimization methods. While ILP provides the optimum results, the CPU time increases exponentially with the number of application nodes. On the other hand, GA-based metaheuristic is faster and determines optimum or near-optimum results in shorter times than ILP. Additionally, we use a selective duplication method to further improve the overall reliability.

How to cite (BibTeX)

@ARTICLE{9290429,

author={Dilek, Selma and Smri, Rawan and Tosun, Suleyman and Dal, Deniz},

journal={IEEE Transactions on Computers},

title={A High-Level Synthesis Methodology for Energy and Reliability-Oriented Designs},

year={2022},

volume={71},

number={1},

pages={161-174},

doi={10.1109/TC.2020.3043885}

}