Projects

Projects by HUEDA Research Group

2023-Ongoing

Developing Topology-Aware Pruning and Mapping Algorithms for Deep Neural Network Accelerators

TÜBİTAK 1001Project No:123R075

Project Title: Developing Topology-Aware Pruning and Mapping Algorithms for Deep Neural Network Accelerators

Principal Investigator: Prof. Dr. Süleyman Tosun

Details

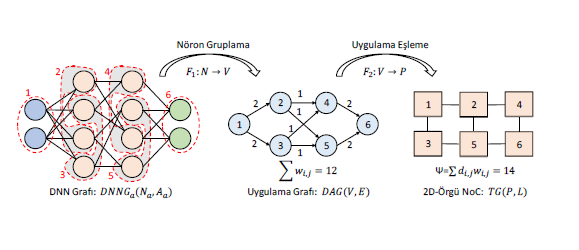

Deep Neural Networks (DNN) have gained wide adoption in various domains in recent years; however, their high computational requirements have made it challenging to implement them in resource-constrained Internet of Things (IoT) devices. DNNs often require multi-processor environments or high-capacity GPU systems, leading to performance loss and high energy consumption, especially when dealing with large data volumes and data transmission between DNN layers. To overcome these limitations, it is crucial to reduce the size of DNN structures without compromising their effectiveness and run them on application-specific architectures optimized for data communication. One promising approach for reducing the size of DNN models is to prune unnecessary model elements, such as weights, neurons, and filters, while maintaining performance. However, DNN models pruned with non-structural methods may be inadequate or even detrimental in architectures designed for standard structures such as CPUs and GPUs.

Therefore, it is more efficient to run pruned models in architectures that offer regular and flexible communication, such as Network-on-Chip (NoC). However, existing pruning methods for DNNs are not optimized for NoC architectures, and there is a need for optimization algorithms that consider the NoC structure and map the pruned system in an energy-efficient manner. In this project, we aim to develop NoC topology-aware heuristic and metaheuristic methods that can perform weight and neuron pruning, optimally group neurons in the pruned DNN structure, and map them to the NoC architecture in an energy-efficient manner.

2017-2019

Reliability-Oriented Design Methods for Application Specific Integrated Circuits

TÜBİTAK-1001Project No:116E095

Project Title:Reliability-Oriented Design Methods for Application Specific Integrated Circuits

Principal Investigator:Assoc. Prof. Dr. Süleyman TOSUN

Details

Ever increasing performance demand from computer applications has resulted in shrinking technology sizes of CMOS circuits every 18 months over the past 40 years. Shrinking technology sizes made it possible to increase the number of transistors on chips. As a result, designers are able to embed more components on a single chip than ever. While smaller transistor sizes reduce the cost of chips as a result of having smaller chip area, the increase in circuit densities makes the design process more challenging than before. Each technology generation also introduces new design problems in digital systems. For example, when the technology sizes are reduced, the circuits become more vulnerable to radiation effects; thus, the transient faults increase in the circuits. While the error correcting codes (i.e., Hamming codes) can be used to reduce the effects of transient errors for memory elements; for combinational circuits, double or triple redundancy-based methods are used to determine the errors. However, redundancy-based error detection methods increase the chip area and the cost.While the reduced technology size makes the circuits more susceptible to transient faults, some energy reduction techniques also negatively affects their reliabilities. For example, when dynamic voltage scaling (DVS) is applied as an energy reduction method, the circuit consumes less energy under lower voltage levels; however, lowering the supply voltage also reduces the reliability of the circuit. When we consider the design of an application with large number of components, tackling all system requirements such as area, performance, energy consumption and reliability may need new systematic design methods. Thus, the design process of application specific integrated circuits (ASICs) must consider all these requirements on higher level of abstraction. High level synthesis (HLS) process aims to integrate all system requirements on higher level of abstraction and remedy the designer from lower level design burdens.

Traditional HLS methods usually consider only area, performance, and energy optimizations and most of the previous work ignore the overall system reliability. Especially, the effect of DVS on reliability is completely ignored by the previous studies when they aim to minimize energy consumption by using DVS. In this work, we aim to develop new HLS methods for ASIC design under area and performance constraints and with low energy consumption and high reliability.

2017-2020

Reconfigurable Network-on-Chips

TÜBİTAK-1001Project No:117E130

Project Title:Reconfigurable Network-on-Chips

Principal Investigator:Assoc. Prof. Dr. Süleyman TOSUN

Details

Network-on-Chip (NoC) is a communication infrastructure for chips consisting too many processing elements. It has been created as a better alternative to classical bus-based communication method and it inherits most of the computer network concepts. When a NoC architecture is designed, the designer should consider performance, cost, fault-tolerance and energy consumption criteria as the chips have limited resources on them. The NoC topology plays an important role to meet the aforementioned criteria of the final network design. For example, a regular topology (such as mesh) might be preferable due to its scalability, fault-tolerance, and reusability for different applications whereas an irregular topology can be favorable due to its huge optimization space for performance, energy, and cost. If we can merge the benefits of these two different topology types, we can have higher chances to meet the required criteria for the applications.Motivated by this observation, in this project, we aim to add reconfigurability to both mesh-based and irregular topology-based NoC designs. We can list the topics and goals of this project as follows:

- Reconfigurable mesh topology design: We plan to add configurable units between the routers of the mesh topology to make it reconfigurable. By changing the unit configuration, we will be able to imitate the mesh topology to be an irregular topology and dynamically change the routing path of a packet in case of network congestion. This will allow us 1) to shut down unused routers to save static energy and 2) to send less data on network resources to save dynamic energy.

- Making mesh topology fault-tolerant: We can tolerate permanent faults as well as transient faults by using reconfiguration capability of meshes. We will design a fault detection mechanism by using parity bits. This unit will detect the fault, its location and type. Using this information, our control mechanism will reroute packets on healthy paths by reconfiguring the configuration units.

- Developing adaptive routing algorithm: We will design an adaptive routing algorithm that dynamically changes the routing paths of the packets by using traffic distribution, faulty path information, and deadlock and livelock conditions of the packets.

- Reconfigurable application-specific topology design: In our previous Tubitak 1001 project, we proposed a method that generates fault tolerant irregular topologies under one permanent link failure. However, in this method, faults must be detected under test during fabrication and can cover only a single link fault. In our current project proposal, we aim to add fault detection mechanism on routers that can detect the multiple faults dynamically when application is running. This fault detection and control unit on a router will also update the routing information of a packet if there is a fault on its path.

- Studying the 3D adaptation of proposed methods: We will investigate the adaptation possibilities of mesh and irregular topology reconfiguration methods and adaptive routing algorithm for 3D NoCs.